- cross-posted to:

- technology@lemmy.world

- cross-posted to:

- technology@lemmy.world

cross-posted from: https://discuss.tchncs.de/post/3011500

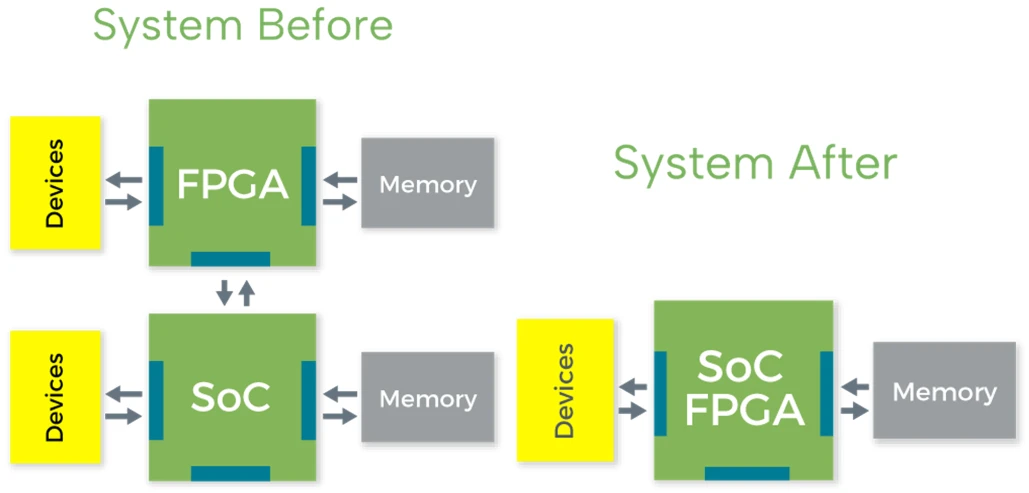

Many volume applications use FPGA because they need in-field reconfigurability (changing standards, changing algorithms, etc) but they want to improve their system’s competitiveness (power, size, cost). FPGAs are bulky, expensive and power hungry. Integrating eFPGA can greatly improve the economics while maintaining full reconfigurability and performance.

We’ve found with customers that a significant portion of the LUTs in their designs don’t change with reconfigurations: they are fixed buses to bring data to and from the reconfigurable core. This can be hardwired so the number of LUTs needed in the SoC is typically half of what’s in the FPGA. There is also a lot of cost of voltage regulators for an FPGA that disappear with integration.

Typically, the cost of eFPGA is 1/10th the cost of the FPGA it replaces but with the same speed and programmability. Power can also be cut to 1/10th because most of the power in an FPGA is the power-hungry PHYs that are mostly not needed when using eFPGA in the SoC.

This makes sense only if you’re rolling your own silicon, and it depends on the application. I could see this as an alternative to a scalar DSP core or to provide more flexible high speed interfaces. The unspoken cost is going to be adding another proprietary set of tooling in the BSP for your chip.